Shift register merupakan rangkaian logika sekuensial yang bisa digunakan untuk menyimpan dan mentransfer data. Rangkaian logika sekuensial ini akan mengambil data dari saluran input dan data tersebut akan dipindahkan ke bagian output dalam setiap kali siklus clock. Pada dasarnya, shift register adalah suatu rangkaian Latch yang disusun dengan membentuk untaian seri sehingga output dari satu Latch akan menjadi input dari Latch berikutnya. Data bisa masuk secara seri satu per satu dari kiri atau pun kanan dan bisa masuk secara bersamaan pada rangkaian paralel.

Biasanya jumlah Latch yang dibutuhkan untuk membuat sebuah shift register ditentukan oleh jumlah bit yang akan disimpan. Sebuah shift register terdiri dari 8 bit atau 1 byte yang tersusun dari 8 Latch. Semua clock yang ada pada setiap Latch dihubungkan menjadi satu clock sehingga perangkat akan sinkron ketika pengoperasian. Shift register digunakan untuk menyimpan data, memindahkan data dan mengubah data dari seri ke paralel atau dari paralel ke seri. Secara umum, shift register dilengkapi dengan sebuah clear dan reset sehingga rangkaian bisa di set atau reset sesuai keinginan. Berdasarkan pergerakan data yang dijalankan, shift register terbagi menjadi 4 kelompok, yaitu :

1. Serial Input to Paralel Output (SIPO)

Data yang masuk ke shift register secara seri, satu bit data untuk setiap siklus clock dan data yang keluar dalam bentuk paralel tanpa mengubah nilai data tersebut.

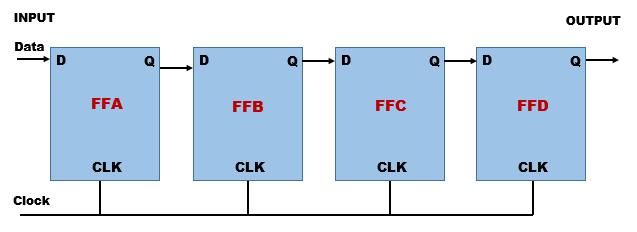

2. Serial Input to Serial Output (SISO)

Data yang masuk ke shift register secara seri dan data yang dikeluarkan juga dalam bentuk seri. Data yang masuk dan keluar dari shift register dikontrol dari clock serta mengubah nilai data tersebut.

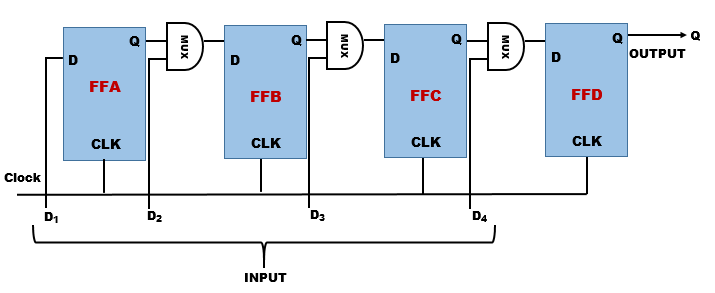

3. Paralel Input to Serial Output (PISO)

Data yang masuk ke shift register dalam bentuk paralel secara bersamaan dalam siklus satu clock. Output berbentuk seri dengan keluaran satu bit untuk setiap clock.

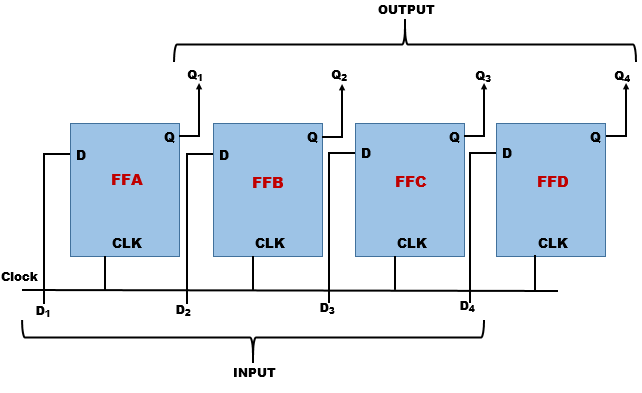

4. Paralel Input to Paralel Output (PIPO)

Data yang masuk ke shift register dalam bentuk paralel secara bersamaan dalam satu siklus clock. Output yang keluar dari shift register juga secara bersamaan untuk siklus clock selanjutnya dan bentuk datanya tetap paralel.

Shift register digunakan untuk memindahkan atau menggeser data menggunakan SIPO dan PISO. Sedangkan SISO dan PIPO digunakan untuk menunda pengeluaran data atau delay.

.png)

No comments:

Post a Comment