Jika suatu garis instruksi harus bercabang dua atau lebih, adakalanya perlu menggunakan bit interlock atau TR untuk menjaga kondisi pada titik percabangan. Hal ini disebabkan karena instruksi dikerjakan dari kiri hingga ke sisi kanan sebelum kembali lagi ke titik percabangan kemudian mengerjakan instruksi pada baris instruksi berikutnya (pada percabangan tersebut). Jika suatu kondisi disisipkan pada garis percabangan instruksi atau disisipkan setelah titik percabangan, maka kondisi eksekusi bisa berubah selama proses tersebut. Sehingga tidak dimungkinkan program berjalan sesuai dengan yang diharapkan. Pada gambar di bawah ini ditunjukkan dua diagram tangga yang sama-sama instruksi 1 dikerjakan terlebih dahulu sebelum instruksi 2.

Pada diagram A, kondisi eksekusi yang muncul pada titik cabang tidak dapat berubah sebelum kembali ke garis percabangan dengan kata lain instruksi 1 tidak dapat mengubah kondisi eksekusi pada titik cabang. Sehingga garis percabangan akan dikerjakan dengan benar. Sedangkan pada diagram B, terdapat sebuah kondisi antara titik cabang dengan instruksi 1. Hal ini menyebabkan kondisi eksekusi sebelum dan setelah kembali ke garis percabangan bisa berbeda, karena instruksi 1 dapat mengubah kondisi eksekusi titik cabang dengan IR000.01-nya jika selama proses ini IR000.01 mengalami perubahan kondisi. Sehinnga tidak mungkin mendapatkan hasil yang diinginkan. Untuk mengatasi hal ini dibutuhkan bit-bit TR atau interlock (IL(02)) atau interlock clear (ILC(03)).

A. Bit-bit TR

Area TR menyediakan 8 bit, TR0 sampai dengan TR7 yang dapat digunakan untuk menyimpan sementara kondisi eksekusi pada titik cabang. Jika sebuah bit TR dipasang pada titik cabang, maka kondisi eksekusi saat itu akan disimpan pada bit TR yang bersangkutan. Saat kembali ke titik cabang, bit TR yang sudah menyimpan kondisi eksekusi sebelumnya, akan dikembalikan kondisi eksekusi seperti semula saat pertama kali eksekusi mencapai titik cabang.

Diagram B yang ditunjukkan pada gambar di atas dapat ditulis ulang dengan benar dengan menggunakan bit TR, sehingga terbentuk diagram tangga untuk diagram B sebagaimana ditunjukkan pada gambar di bawah ini. Diawali dengan menuliskan sambungan ke IR00.00 dilanjutkan mengeluarkan hasil kondisi eksekusinya ke TR0 (alamat 00000 dan 00001). Kemudian diteruskan dengan AND pada IR000.01 hingga instruksi 1 (alamat 00002 dan 00003). Untuk garis cabang yang bawah diawali dengan LD untuk TR0 dan AND untuk IR000.02 hingga instruksi 2 (alamat 00004 hingga 00006).

Dalam hal ini instruksi 1 akan berstatus ON jika TR0 dan IR000.01 keduanya juga berstatus ON. Demikian juga dengan instruksi 2, akan berstatus ON jika TR0 dan IR000.02 keduanya berstatus ON juga.

Pada gambar di bawah ini ditunjukkan contoh penggunaan dua buah bit TR (TR0 dan TR1). Pada contoh diagram tangga ini, TR0 dan TR1 digunakan untuk menyimpan kondisi eksekusi di dua titik cabang. Setelah mengerjakan instruksi 1, TR1 akan mengembalikan kondisi eksekusi di titik cabang yang bersangkutan yang kemudian di-AND-kan dengan IR000.03 untuk menentukan kondisi eksekusi bagi instruksi 2. Sedangkan bit TR0 digunakan dua kali. Pertama, saat instruksi 1 dan instruksi 2 selesai dikerjakan, maka eksekusi akan kembali ke titik cabang dan menggunakan TR0 pertama kali untuk di-AND-kan dengan IR000.04 untuk menentukan kondisi eksekusi instruksi 3. Kedua, setelah selesainya eksekusi instruksi 3 dan menggunakan bit TR0 kedua kali di-AND-kan dengan IR000.05 untuk menentukan kondisi eksekusi instruksi 4.

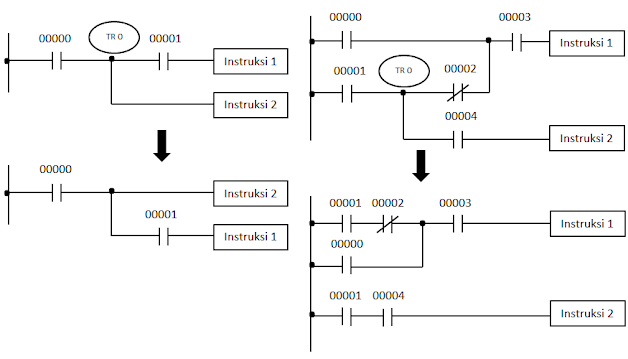

Yang perlu diperhatikan disini adalah Anda bisa menggunakan sebanyak mungkin bit TR (hanya ada 8) untuk keperluan titik cabang. Tetapi hindari penggunaan bit TR yang sama untuk dua titik cabang atau lebih pada blok instruksi yang sama. Jika ada lebih dari 8 titik cabang maka disarankan menggunakan bit interlock. Selain itu gunakan bit TR sebijaksana mungkin, kalau diagram tangga bisa disederhanakan tanpa melibatkan bit TR maka lakukanlah. Hal ini dimaksudkan untuk mengurangi kerumitan program mnemoniknya sedikit susah dibaca. Perhatikan contoh cara penyederhaan yang ditunjukkan pada gambar di bawah ini.

Sebagaimana ditunjukkan pada gambar di atas, diagram tangga di sebelah kiri bisa disederhanakan dengan cara mengubah urutan penempatan instruksi 1 dan 2. Selain tidak membutuhkan bit TR, kode mnemoniknya juga lebih sederhana. Sedangkan diagram tangga yang sebelah kanan bisa disederhanakan dengan cara memisahkan keluaran ke instruksi 2 dan menggunakan instruksi LD untuk menggantikan titik cabang.

Catatan :

1. Walaupun penyederhaan diagram tangga selalu diperhatikan, urutan eksekusi instruksi kadangkala perlu diperhatikan juga. Misalnya, sebuah instruksi MOV dibutuhkan sebelum suatu instruksi ADD (secara biner) dikerjakan untuk menempatkan data ke operan yang terkait. Dengan demikian pastikan Anda selalu memperhatikan urutan eksekusi sebelum menyederhanakan diagram tangga.

2. Bit TR hanya bisa dituliskan melalui kode mnemonik. Anda tidak perlu menuliskannya jika pembuatan diagram tangganya secara langsung karena akan ditulis secara otomatis. Perlu juga diperhatikan batasan jumlah bit TR yang bisa digunakan (hanya 8 saja) dan mengurangi jumlah instruksi program.

B. Bit-bit Interlock

Selain menggunakan bit-bit TR, instruksi INTERLOCK (IL(02)) dan INTERLOCK CLEAR (ILC(03)) dapat digunakan. Instruksi ini digunakan dengan cara mengeliminasi atau menghilangkan titik-titik cabang yang ada. Instruksi INTERLOCK dan INTERLOCK CLEAR digunakan bersamaan.

Jika instruksi INTERLOCK ditempatkan sebelum suatu bagian atau seksi lain program atau diagram tangga, maka kondisi eksekusi dari INTERLOCK tersebut akan digunakan untuk semua instruksi hingga dijumpai instruksi INTERLOCK CLEAR. Jika kondisi eksekusi INTERLOCK adalah ON, maka garis instruksi berikutnya dan seterusnya hingga dijumpai INTERLOCK CLEAR akan diawali dengan kondisi eksekusi ON juga.

Sebagaimana ditunjukkan pada gambar di bawah ini, diagram B pada gambar di atas dapat dikoreksi menggunakan instruksi INTERLOCK. Pada gambar di bawah ini kondisi eksekusi IR000.00 akan menentukan kondisi eksekusi (IL(02)), kemudian instruksi 1 dan 2 masing-masing diawali dengan kondisi eksekusi INTERLOCK (IL(02)) sebelum masing-masing melalui IR000.01 dan IR000.02 karena setelah itu diakhiri dengan INTERLOCK CLEAR (IL(03)).

Contoh lainnya ditunjukkan pada gambar di bawah ini. Pada diagram tangga tersebut terdapat dua INTERLOCK. Dalam hal instruksi 1 hanya dipengaruhi oleh INTERLOCK yang pertama saja. Sedangkan instruksi 2,3 dan 4 dipengaruhi oleh INTERLOCK yang pertama dan kedua. Sehingga, jika IR000.00 menyebabkan IL(02) menjadi OFF maka instruksi 1 hingga 4 tidak akan dijalankan (OFF). Tetapi jika IR000.00 menyebabkan IL(02) menjadi ON, maka instruksi 1 dikerjakan dahulu (sesuai dengan gabungan IL(02) dan IR000.01) dan IL(02) akan memiliki kondisi eksekusi yang sesuai dengan gabungan IL(02) yang pertama dan IR000.02. Jika akibatnya IL(02) yang kedua OFF, maka instruksi 2 hingga 4 tidak dikerjakan. Tetapi jika IL(02) yang kedua ON, maka instruksi 2 hingga 4 akan dikerjakan sesuai dengan kondisi eksekusi dari IR000.03, IR000.04, IR000.05 dan IR000.06 masing-masing.

.png)

No comments:

Post a Comment